# **Optimizing Tensor Contractions for Embedded Devices with Racetrack and DRAM Memories**

ASIF ALI KHAN and NORMAN A. RINK, Technische Universität Dresden, Germany FAZAL HAMEED, Institute of Space Technology, Islamabad, Pakistan JERONIMO CASTRILLON, Technische Universität Dresden, Germany

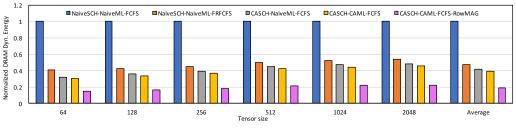

*Tensor contraction* is a fundamental operation in many algorithms with a plethora of applications ranging from quantum chemistry over fluid dynamics and image processing to machine learning. The performance of tensor computations critically depends on the efficient utilization of on-chip/off-chip memories. In the context of low-power embedded devices, efficient management of the memory space becomes even more crucial, in order to meet energy constraints. This work aims at investigating strategies for performance- and energy-efficient tensor contractions on embedded systems, using *racetrack memory* (RTM)-based *scratch-pad memory* (SPM) and DRAM-based off-chip memory. Compiler optimizations such as the loop access order and data lay-out transformations paired with architectural optimizations for off-chip memory such as memory access order, data mapping and the choice of a suitable memory access granularity are employed to reduce the contention in the off-chip memory. Experimental results demonstrate that the proposed optimizations improve the SPM performance and energy consumption by 32% and 73%, respectively, compared to an iso-capacity SRAM. The overall DRAM dynamic energy consumption improvements due to memory optimizations amount to 80%.

$\label{eq:ccs} COS \ Concepts: \bullet \ Hardware \rightarrow Emerging \ architectures; \bullet \ Computer \ systems \ organization \rightarrow Embedded \ systems; \bullet \ Software \ and \ its \ engineering \ \rightarrow \ Source \ code \ generation;$

Additional Key Words and Phrases: Compiler optimization, data transformation, tensors, tensor contraction, matrix multiplication, racetrack memory, preshifting, prefetching, embedded systems, DRAM mapping

#### **ACM Reference format:**

Asif Ali Khan, Norman A. Rink, Fazal Hameed, and Jeronimo Castrillon. 2020. Optimizing Tensor Contractions for Embedded Devices with Racetrack and DRAM Memories. *ACM Trans. Embed. Comput. Syst.* 19, 6, Article 44 (September 2020), 26 pages. https://doi.org/10.1145/3396235

**1 INTRODUCTION**

Tensors are multi-dimensional data structures that generalize matrices. Consequently, tensor contraction generalizes the operation of matrix multiplication. The abstractions offered by tensors

© 2020 Copyright held by the owner/author(s). Publication rights licensed to ACM.

$1539 \hbox{-} 9087/2020/09 \hbox{-} ART44 \ \$15.00$

https://doi.org/10.1145/3396235

This work was partially funded by the German Research Council (DFG) through the TraceSymm project CA 1602/4-1 and the Cluster of Excellence 'Center for Advancing Electronics Dresden' (cfaed).

Authors' addresses: A. A. Khan, N. A. Rink, and J. Castrillon, Technische Universität Dresden, 01069, Dresden, Germany; emails: {asif\_ali.khan, norman.rink, jeronimo.castrillon}@tu-dresden.de; F. Hameed, Institute of Space Technology, 44000, Islamabad, Pakistan; email: fazal.hameed@ist.edu.pk.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

Fig. 1. Applications domains for embedded systems in the Internet of Things.

and their operations are central to many algorithms in modern application domains such as signal and media processing, computer vision, and machine learning. Recent years have seen a surge in the emergence of new programming languages and frameworks specifically designed for the handling of tensor-based computations in these application domains [1, 5, 30, 52], also targeting heterogeneous platforms, e.g., [11] and [29]. In the age of the *Internet of Things*, media processing, computer vision, and machine learning are key application domains for embedded devices, which enable ubiquitous computing in environments that call for extremely low energy footprint and tiny form factors. Examples of such environments are wearables and autonomous vehicles or aircraft, where tensor processing on the device allows for efficient inference in intelligent applications, cf. Figure 1.

The typical constraints on size, power, and energy consumption in the embedded domain make the design of systems for processing large multi-dimensional tensors especially challenging. Particular pressure is put on the design of the memory subsystem, which must accommodate large tensorial data structures within the given constraints. This pushes traditional approaches and technologies to their limits. For example, as was already observed in the mid-2000s, traditional SRAM-based memory is power hungry and suffers from severe leakage power consumption that is responsible for up to 33.7% of the total memory energy consumption [22, 23]. Similarly, the data mapping and the memory access order, if not managed properly, not only degrade performance but also exacerbate energy consumption.

A radically new approach to the design of memory hierarchy is to use a combination of DRAM and NVM memories to exploit their relative benefits while avoiding their disadvantages. One particularly promising NVM technology is the spin-orbitronics-based racetrack memory (RTM), which is more reliable and has lower read/write latency than alternative NVM technologies [6, 43, 44]. Moreover, RTM is very energy-efficient, which is why it is particularly interesting for deployment in embedded devices. This article extends the work in [28] and proposes data layouts and architecture support for optimizing the important tensor contraction operation for RTM-based *scratch-pad* memory (SPM) in conjunction with DRAM-based off-chip memory.

Unlike conventional memories, a single memory cell in RTM stores data in a tape-like magnetic nanowire called *track*. Each track is equipped with a read/write port, and accessing data on a track requires shifting and aligning it to the port position. If the programmer or compiler does not manage data layout judiciously, additional shifts become necessary which degrade performance and energy efficiency. Similarly, to reduce contention in the off-chip DRAM, it is important to devise contention-aware techniques that take into account the underlying DRAM architecture and the tensor data.

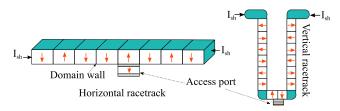

Fig. 2. RTM horizontal and vertical placement.

Specifically, this article makes the following contributions.

- (1) For tensors that fit entirely into the SPM, we derive a data layout that reduces the number of shifts necessary for a tensor contraction to the absolute minimum.

- (2) We discuss how contractions of large tensors are handled by processing tiles of the tensors in SPM. We show how, in the presence of tiling, the number of shifts can also be reduced to the bare minimum by switching the data layout when bringing new tiles into the SPM.

- (3) We present an optimized mapping of tensor data to off-chip DRAM that saves energy by reducing the number of DRAM operations compared to a conventional tensor mapping.

- (4) We propose a contention-aware memory access schedule that reduces the impact of different contentions (i.e., read-write interference and row buffer conflict) in DRAM memory by efficiently overlapping computation with memory access that simultaneously improves performance and energy efficiency.

- (5) We investigate the impact of large memory access granularity on performance and energy consumption. We found that a large memory access granularity saves energy compared to a smaller one when using our contention-aware memory access schedule and layout.

The rest of this article is organized as follows: Section 2 gives a brief overview of the RTM technology, the SPM layout, off-chip memory, and the tensor contraction operation. Section 3 discusses how various SPM data layouts impact the overall shifting overhead in RTM and presents the best data layout for tensor contraction. Section 4 explains the proposed contention-aware memory layout and efficient scheduler for the off-chip memory. Section 5 and Section 6 provide the evaluation results and comparison with the state-of-the-art. Section 7 discusses the state of the art and Section 8 concludes the article.

## 2 BACKGROUND

This section briefly explains the working principle and architecture of racetrack and DRAM memories. In addition, it provides background on the tensor contraction operation and layout of scratchpad memories.

## 2.1 Racetrack Memory

Racetrack memories have evolved significantly over the last decade. Unlike in conventional memories, a single cell in RTM is a magnetic nano-wire (track) that can have up to 100 magnetic *domains* where each domain represents a bit. Domains in a nano-wire are separated by magnetic domain walls (DWs). The track can be placed vertically (3D) or horizontally (2D) on the surface of a silicon wafer as shown in Figure 2. While the vertical placement of tracks achieves the storage density of today's magnetic disk drives, it faces several design challenges. In the horizontal configuration, the

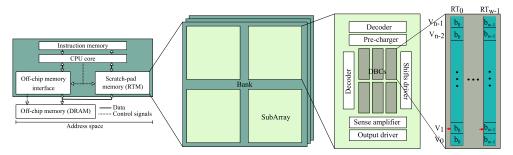

Fig. 3. System and scratch-pad memory architecture.

cell size can be much smaller than the smallest memory cell today. With state-of-the-art materials, the RTM cell size can be  $1.5 \text{ F}^2$  compared to  $120-200 \text{ F}^2$  in SRAM and  $4-8 \text{ F}^2$  in DRAM [37, 53].

#### 2.2 Scratch-Pad Memory

Scratch-pad memory is a faster on-chip memory, usually based on SRAM. Compared to hardwaremanaged on-chip caches, the SPMs, which are managed by software (i.e., by the programmer or compiler), offer a number of advantages. SPMs have relatively simple architecture and do not require the complex peripheral circuitry of caches; saving both area and energy. SPMs do not need any tag comparison, making access to the on-chip memory faster. Particularly in the embedded domain, SPMs perform better than caches because embedded applications often have regular memory access patterns. With SPMs, it is very easy to efficiently choreograph the data movement between the on-chip and off-chip memories. This also enables better predictability of the application timings, a key feature of embedded systems.

Figure 3 shows a typical embedded system architecture with the address space partitioned between the off-chip memory and the SPM. Typically, the off-chip memory is accessed via cache. However, in this work, we are only interested in the data layout in SPM and the data movement between the off-chip memory and SPM. Therefore, we drop the on-chip cache from our design consideration. We assume that scalar variables can be stored in registers and only focus on the tensor layouts in SPM. SPMs have been successfully used already in the design of accelerators for machine learning, e.g., in [10].

Figure 3 also shows the detailed SPM architecture. Since the typical SRAM-based SPMs have small capacity [10], we consider a comparable 48 KiB SPM which is divided into three banks. Each bank stores one tensor and is made up of 64 *domain wall block clusters* (DBCs). A DBC is a group of *w* tracks with each track storing *n* domains. Similar to [56], we assume that each *w*-bit value is stored in an interleaved fashion across the *w* tracks of a DBC and that the tracks in DBC can be moved together in a lock-step fashion. For this work, we assume one access port per track (pointing to location 0 initially), *dynamic* port access policy and *lazy* port update policy [6]. Further, we consider *w* equals 32 and *n* to be 64. This implies that each bank in the SPM can store a  $64 \times 64$  tensor. Larger tensors can be partitioned into *tiles*, as explained in Section 3.4.

#### 2.3 Off-Chip Memory (DRAM)

A typical DRAM memory is a hierarchical pyramid of structures composed of channels, banks, rows, columns, and cells. Each (channel, bank, row, column) consists of many (banks, rows, columns, cells), respectively. Each bank contains a *row buffer* that keeps the recently accessed row from the bank. The DRAM controller issues one or many commands to read/write data to/from DRAM memory. A *precharge* (PRE) command is required to make the bank ready for a new

access. This command is not issued in the scenario when the bank is already in the *precharged* state. An *activate* (ACT) command is required to fetch the relevant row to the row buffer of the DRAM bank. A DRAM *row buffer hit* occurs when the requested row resides in the row buffer. In this scenario, the controller does not issue the *activate* command. A DRAM *row buffer conflict* occurs when a request is made to a row  $Row_i$  of the bank while another row  $Row_j$  resides in the row buffer. Finally, a *read/write* command is issued to access the requested data from the row buffer when the desired row exists in the row buffer. A DRAM row buffer conflict causes high DRAM energy consumption compared to a row buffer hit. This is due to the fact that the DRAM controller issues more commands (precharge, activate, and read/write) to service a request with a row buffer conflict compared to a row buffer hit (i.e., read/write) request.

Read-write interference occurs in DRAM due to read-to-write and write-to-read penalties in terms of latency and energy. Read-to-write latency is the minimum latency between a read request and write request which is incurred to change the mode of the DRAM channel pins from read to write state. Therefore, the DRAM channel will be idle during this time. Write-to-read latency is the latency incurred to change the mode of the DRAM channel from the write to read state plus an additional latency required to correctly update the data in the row buffer. The write-to-read latency is higher compared to read-to-write latency which makes the DRAM channel idle for a longer duration.

#### 2.4 Tensor Contraction

Tensors are multi-dimensional data structures. Special cases of tensors are vectors (1-dimensional tensors) and matrices (2-dimensional tensors). Matrix-vector and matrix-matrix multiplication are low-dimensional instances of the more general operation of tensor contraction. To introduce tensor contractions, let us consider the example of a 5-dimensional tensor A and a 3-dimensional tensor B. Five indices are required to access an entry in A, and the entry at indices  $i_1, i_2, i_3, i_4, i_5$  is denoted as  $A_{i_1i_2i_3i_4i_5}$ . Analogously,  $B_{i_6i_7i_8}$  is an entry in the tensor B, at indices  $i_6, i_7, i_8$ . Each index can take values in a fixed integer domain, say  $i_{\alpha} \in \{1, \ldots, M_{\alpha}\}$  for  $\alpha = 1, \ldots, 8$ . The  $M_{\alpha}$  are the *dimensions* of the tensors A and B. That is, A has dimensions  $M_1, M_2, M_3, M_4, M_5$ , and B has dimensions  $M_6, M_7, M_8$ . An example contraction of A and B along two dimensions is the following sum-of-products that yields a tensor C,

$$C_{j_1 j_2 j_3 j_4} = \sum_{n=1}^{M_5} \sum_{m=1}^{M_2} A_{j_1 m j_2 j_3 n} \cdot B_{j_4 m n}.$$

(1)

Here the contraction is over the dimensions indexed with m and n. For this contraction to make sense, certain dimensions of A and B must match. Specifically,  $M_2 = M_7$  and  $M_5 = M_8$  must hold. In other words, the pairs of dimensions that are indexed with m and n, respectively, must match. The tensor C that results from the contraction in Equation (1) then is 4-dimensional, with dimensions  $M_1, M_3, M_4, M_6$ .

Equation (1) can be rearranged to emphasize that tensor contraction is indeed a generalized version of matrix multiplication. To this end, let  $\tilde{A}$ ,  $\tilde{B}$  be tensors that are obtained from A, B by permuting indices as follows:

$$\begin{split} \hat{A}_{i_1 i_3 i_4 i_2 i_5} &= A_{i_1 i_2 i_3 i_4 i_5}, \\ \tilde{B}_{i_7 i_8 i_6} &= B_{i_6 i_7 i_8}. \end{split}$$

The same tensor *C* as in Equation (1) is obtained by contracting  $\tilde{A}$  and  $\tilde{B}$  as follows:

$$C_{j_1 j_2 j_3 j_4} = \sum_{n=1}^{M_5} \sum_{m=1}^{M_2} \tilde{A}_{j_1 j_2 j_3 mn} \cdot \tilde{B}_{mn j_4}.$$

(2)

If indices are further arranged into groups  $k_1$ ,  $k_3$ , l such that  $k_1 = (j_1 j_2 j_3)$ ,  $k_3 = (j_4)$ , and l = (m n), then C can be written as

$$C_{k_1k_3} = \sum_{l=1}^{M_2 \cdot M_5} \tilde{A}_{k_1l} \cdot \tilde{B}_{lk_3}.$$

(3)

Equation (3) is readily recognized as matrix multiplication.

Reorganizing the tensor contraction from Equation (1) into the form of matrix multiplication is a standard trick that is commonly referred to as TTGT, e.g., [50]. The key problem with TTGT is that the reorganization of the original tensors A, B into  $\tilde{A}$ ,  $\tilde{B}$  requires costly transposition operations, i.e., costly changes of data layout. Moreover, the need for the new tensors  $\tilde{A}$ ,  $\tilde{B}$  in TTGT doubles the memory footprint of tensor contraction. In the presence of SPM, the copying of tensors to the SPM is necessary anyway before the contraction operation itself can be carried out. This offers an opportunity for hiding the latency of transposition, provided transfers between off-chip memory and the SPM have uniform latency and can be carried out with a stride.<sup>1</sup>

#### 3 SPM LAYOUT FOR MINIMAL SHIFTING

In this section, we explain the impact that data layout and access order in RTM-based SPM have on the shifting overhead. We move from a naive layout to an optimized layout by successively removing unnecessary shifts that do not do any useful work. To process large tensors in the SPM, they must be broken up into tiles. Switching between tiles generally comes with a latency but also offers further opportunities for reducing the number of shifts by overlapping data transfers and computation, and for latency hiding by prefetching.

#### 3.1 Overview

The operation we implement for SPM is tensor contraction in the form specified by Equation (3). If the dimensions of tensors  $\tilde{A}$ ,  $\tilde{B}$  are very small, these tensors can fit entirely in the SPM. We focus on this situation in Sections 3.2 and 3.3, deriving an optimized data layout and access order for a minimal number of shifts.

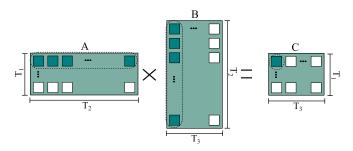

However, in the relevant application domains of media processing and machine learning, tensors are typically large to begin with. Even if one starts out with moderately sized tensors, after grouping dimensions as in the derivation of Equation (3), the resulting matrices  $\tilde{A}_{k_1l}$ , and  $\tilde{B}_{lk_3}$  will have large dimensions. To still carry out tensor contraction with a fixed-size SPM, the tensors involved must be *tiled* [39] (or *blocked* [2]).

We assume that the SPM can fit three quadratic  $n \times n$ -matrices. Then, the tensors  $\tilde{A}$ ,  $\tilde{B}$ , and C must be divided into tiles of size  $n \times n$ . To ease the discussion of tiling, we introduce new labels for the dimensions of  $\tilde{A}$ ,  $\tilde{B}$ , and C in Equation (3):

| dimensions of $\tilde{A}$ : | $N_1, N_2$ |

|-----------------------------|------------|

| dimensions of $\tilde{B}$ : | $N_2, N_3$ |

| dimensions of $C$ :         | $N_1, N_3$ |

<sup>&</sup>lt;sup>1</sup>One typically speaks of *gather* and *scatter* accesses to memory when referring to reads or writes with a stride.

44:6

ACM Transactions on Embedded Computing Systems, Vol. 19, No. 6, Article 44. Publication date: September 2020.

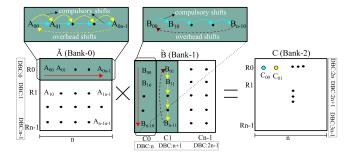

Fig. 4. Tensor contraction with a naive memory layout.

We further assume that *n* evenly divides these dimensions, i.e., that there are natural numbers  $T_1, T_2, T_3$  such that  $N_1 = T_1 \cdot n$ ,  $N_2 = T_2 \cdot n$ , and  $N_3 = T_3 \cdot n$ . If this is not the case initially, one can always pad  $\tilde{A}$ ,  $\tilde{B}$ , and C with rows or columns of zeros, which does not affect the result of tensor contraction.<sup>2</sup> The tensor C now consists of  $T_1 \times T_3$  tiles,  $\tilde{A}$  of  $T_1 \times T_2$  tiles, and  $\tilde{B}$  of  $T_2 \times T_3$  tiles, and the tiled version of Equation (3) is:

$$C_{(t_1 \cdot n + k_1)(t_3 \cdot n + k_3)} = \sum_{t=0}^{T_2 - 1} \sum_{l=1}^n \tilde{A}_{(t_1 \cdot n + k_1)(t \cdot n + l)} \cdot \tilde{B}_{(t \cdot n + l)(t_3 \cdot n + k_3)}.$$

(4)

For a fixed value of t (in the outer summation), the inner summation (over l) can now be carried out inside the SPM. When the inner summation for fixed t has been completed, new tiles of  $\tilde{A}$  and  $\tilde{B}$  must be brought into the SPM. Specifically, the tiles for the next value of t, i.e., t + 1, are needed. The tile of C stays in the SPM and accumulates the results of the inner summations for each fixed  $t = 0, \ldots, (T_2 - 1)$ . The tile of C is written back to off-chip memory only after all summations over t and l have been completed. At this point, the evaluation of tensor contraction moves on to the next entry in the rows or columns of tiles of C.

As we will see in Section 3.2, a sizeable portion of the shifts in tensor contraction may be spent on resetting access ports of DBCs to their initial positions for processing again a row of  $\tilde{A}$  or a column of  $\tilde{B}$  that has previously been traversed in computing an entry of C. While Section 3.3 discusses how the portion of these shifts can be reduced, Section 3.4 demonstrates how unnecessary shifts can be fully eliminated in tiled tensor contraction. Section 3.5 explains that although *prefetching* parts of the next tiles cannot further reduce the number of shifts, it can hide latencies in the full tensor contraction operation. The same statement applies to *preshifting*, cf. Section 3.6.

#### 3.2 Naive SPM Layout

In a naive layout, the tensors  $\tilde{A}$ ,  $\tilde{B}$ , and C are stored in RTM in their order of access. Specifically, tensor  $\tilde{A}$  is accessed row-wise and is stored in the RTM with each DBC storing one row. Similarly, tensor  $\tilde{B}$  is accessed column-wise and is stored column-wise in DBCs. The resultant tensor C is computed and stored row-wise. Figure 4 sketches this layout, which is assumed to be the starting point for the tensor contraction operation. All access ports of all DBCs are aligned with the first entries in rows (for  $\tilde{A}$  and C) or the first entries in columns (for  $\tilde{B}$ ).

To compute the entry  $C_{00}$  in the resultant tensor C, the first row of  $\tilde{A}$  (stored in DBC-0) is multiplied with the first column of  $\tilde{B}$  (stored in DBC-n). More explicitly,  $\tilde{A}_{00}$  is multiplied with  $\tilde{B}_{00}$  and both DBCs are shifted once so that the access ports point to next elements  $\tilde{A}_{01}$  and  $\tilde{B}_{10}$ .

<sup>&</sup>lt;sup>2</sup>This is because contraction is a *linear* operation.

respectively. Next,  $\tilde{A}_{01}$  and  $\tilde{B}_{10}$  are multiplied and the DBCs are shifted once again. This continues until  $\tilde{A}_{0(n-1)}$  and  $\tilde{B}_{(n-1)0}$  are reached and multiplied. The blue arrows in Figure 4 demonstrate this process that results in the entry  $C_{00}$  of the tensor C, which is marked by a blue dot. At this point, each of DBC-0 and DBC-n have been shifted n-1 times, resulting in a total number of 2(n-1)shifts. These shifts cannot be avoided as they are required to access the entries in the first row of  $\tilde{A}$  and the first column of  $\tilde{B}$ . Hence, we refer to these shifts as *compulsory shifts*.

The access ports of both DBC-0 and DBC-n now point to locations n - 1. Before computing  $C_{01}$ , DBC-0 needs to be shifted n - 1 times in order to align its access port to location 0, i.e., to the entry  $\tilde{A}_{00}$ . These shifts do not perform any useful work, and we call them *overhead shifts*. With these overhead shifts, the total amount of shifts increases to 2(n - 1) + (n - 1). The exact same process is repeated to compute the remaining n - 1 elements in the first row of tensor *C*. After computing the last element ( $C_{0n-1}$ ) in the first row of *C*, the port position of DBC-0 is restored to position 0. Thus, the total amount of shifts required for computing R0 in *C* is

Shifts'<sub>R0</sub> =

$$2n(n-1) + n(n-1)$$

, (5)

with the second term in the expression on the right-hand side representing the overhead shifts.

After computing the first row of *C*, the access ports of all DBCs of tensor  $\hat{B}$  point to location n - 1. They must be shifted back to location 0 before the computation of the next row of *C* can start. This incurs n(n - 1) overhead shifts. The updated sum of the total number of shifts then becomes

$$\text{Shifts}_{R0} = \underbrace{2n(n-1)}_{\text{compulsory shifts}} + \underbrace{n(n-1) + n(n-1)}_{\text{overhead shifts}}.$$

(6)

Computing each of the remaining n - 1 rows of *C* incurs the same amount of shifts, leading to the total number of shifts required for contracting the  $n \times n$  tensors  $\tilde{A}$ ,  $\tilde{B}$ ,

Total shifts' =

$$n \cdot (\underbrace{2n(n-1)}_{\text{compulsory shifts}} + \underbrace{2n(n-1)}_{\text{overhead shifts}}).$$

(7)

For writing the entries of *C*, which result from the computations, n(n - 1) compulsory shifts are needed. The same amount of overhead shifts is required to reset the port position to location 0 in all DBCs for tensor *C*. Adding these to Equation (7) and expanding yields

$$\text{Total shifts (naive)} = \underbrace{2n^3 - n^2 - n}_{\text{compulsory shifts}} + \underbrace{2n^3 - n^2 - n}_{\text{overhead shifts}}$$

(8)

From Equation (8), it is clear that half of the total number of shifts are overhead shifts. Thus, avoiding the overhead shifts can improve the memory system's performance by as much as  $2\times$ .

#### 3.3 Optimized SPM Layout

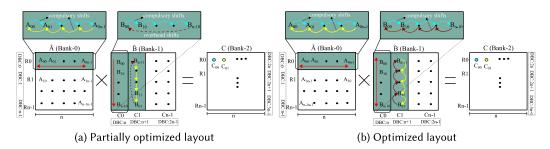

The large proportion of overhead shifts in the naive layout of tensors in the RTM occur due to the uni-directional accesses of the tensors' entries: rows of  $\tilde{A}$  are always accessed from left-to-right and columns of  $\tilde{B}$  from top-to-bottom. In this section, we eventually fully eliminate the overhead shifts by laying out tensors in the RTM so that bi-directional accesses become possible.

First, instead of always accessing R0 of A from left to right to compute a new entry in the first row of C, we can access R0 in a back and forth manner, and thus completely avoid the overhead shifts for R0. Specifically, after computing  $C_{00}$ , the access port of DBC-0 is not reset to location 0. Instead,  $C_{01}$  is computed by accessing the elements of R0 (in  $\tilde{A}$ ) in the reverse order. For this to

Fig. 5. Tensor contraction with the partially optimized and optimized memory layouts (note the layouts and access orders of R1 in  $\tilde{A}$  and C1 in  $\tilde{B}$ ).

produce the correct result, the column C1 of  $\tilde{B}$  must be stored in reverse order in DBC-(n+1), as depicted in Figure 5(a). Note that this way of computing  $C_{01}$  relies on the associativity of addition.<sup>3</sup>

The same procedure works for the computations of all elements of *C*, provided the columns of  $\tilde{B}$  are stored in DBC-n to DBC-(2n-1) with alternating directions. Since the rows of  $\tilde{A}$  are now accessed in a back-and-forth manner, no overhead shifts are incurred for accessing  $\tilde{A}$ . However, the DBCs that store the columns of  $\tilde{B}$  must be fully reset after computing each row of *C*, leading to a total of n(n - 1) overhead shifts per row of *C*. The numbers of compulsory and overhead shifts required for accesses to *C* are the same as in the naive layout. Thus, the total number of shifts for the alternating layout of columns of  $\tilde{B}$  is

$$\text{Total shifts (partial-opt)} = \underbrace{2n^3 - n^2 - n}_{\text{compulsory shifts}} + \underbrace{n^3 - n}_{\text{overhead shifts}}, \qquad (9)$$

which one arrives at by subtracting the  $n^2(n-1)$  overhead shifts for resetting the rows of  $\tilde{A}$  from the right-hand side of Equation (8).

The vast majority of overhead shifts in the previously discussed alternating column layout of B occurs when the computation of one row of C has been completed and one advances to the next row. At this point, all access ports for the DBCs that store columns of  $\tilde{B}$  point to the last entry in each column. To compute the next row of C, the next row of  $\tilde{A}$ , say R1, must be multiplied into the columns of  $\tilde{B}$ . The access port for DBC-1 points to the first entry in R1 of  $\tilde{A}$ , which necessitates that the access ports for the columns of  $\tilde{B}$  (DBC-n to DBC-(2n-1)) be reset to point at the first entry of the columns. However, this resetting of DBC-n to DBC-(2n-1) can be avoided, if the next row of  $\tilde{A}$  is stored in reverse order. Then, multiplication of R1 into a column of  $\tilde{B}$  can be carried out in a backwards fashion. This alternating row layout for  $\tilde{A}$  is depicted in Figure 5(b), in combination with the alternating column layout of  $\tilde{B}$ . The total number of shifts is now comprised of the compulsory shifts and only those n(n - 1) overhead shifts that are needed to reset the DBCs for the rows of C after the full contraction operation has been completed, i.e.,

Total shifts (opt) =

$$\underbrace{2n^3 - n^2 - n}_{\text{compulsory shifts}} + \underbrace{n^2 - n}_{\text{overhead shifts}}$$

. (10)

Note, in particular, that no overhead shifts are required to reset the DBCs for  $\tilde{A}$ ,  $\tilde{B}$  after completing the full tensor contraction. Since the rows of  $\tilde{A}$  and the columns of  $\tilde{B}$  are traversed in a back and forth manner, the access ports for their DBCs point back to the first entries in the rows of

<sup>&</sup>lt;sup>3</sup>For floating-point numbers, associativity of addition is typically also assumed when aggressive compiler optimizations are enabled with *fast-math* compiler flags.

Fig. 6. Tile-wise tensor contractions (tile-size:  $n \times n$ ).

$\tilde{A}$  and columns of  $\tilde{B}$ , respectively, exactly when the computation of the last entry in *C* has been completed. This reasoning relies on *n* being even. In practice, *n* is actually a power of two, for efficient utilization of address bits.

By comparing Equation (10) with the corresponding equation for the naive layout, i.e., Equation (8), we see that the alternating row and column layout asymptotically cuts the total number of shifts necessary to implement tensor contraction in half.

#### 3.4 Contraction of Large Tensors

We now use the optimized layout from the previous section to optimize the number of shifts needed for contracting large tensors that must be processed in the SPM tile by tile, as explained in Section 3.1. Equation (3) says that each pair of tiles from  $\tilde{A}$  and  $\tilde{B}$  is contracted exactly as discussed in the previous sections, where it was assumed that  $\tilde{A}$  and  $\tilde{B}$  fit entirely into the SPM. Equation (3) also says that each tile of C is computed by accumulating the results of contracting a row of tiles of  $\tilde{A}$  with a column of tiles of  $\tilde{B}$ . This is depicted by Figure 6, where  $T_1, T_2, T_3$  are the respective numbers of tiles in each dimension, as in Section 3.1.

Based on Equation (10), the overall number of shifts needed to contract all tiles of  $\tilde{A}$  with all tiles of  $\tilde{B}$  is

Shifts'<sub>tiled</sub> =

$$T_1 T_2 T_3 \cdot \left\{ (2n^3 - n^2 - n) + (n^2 - n) \right\}.$$

(11)

This accounts for resetting the access ports of the DBCs that hold a tile of *C* after the contraction of each pair of tiles of  $\tilde{A}$ ,  $\tilde{B}$ . What is not yet accounted for are the number of shifts needed to bring new tiles into the SPM.

To copy a new tile of A or B into the SPM, n(n-1) compulsory shifts are required. The same number of shifts is needed to reset the access ports for the newly copied tile. The computation of each new tile of C must start with a zero-initialized tile. This initialization requires again n(n-1)compulsory shifts and n(n-1) overhead shifts. After the computation of a tile of C has completed, the tile must be copied back to off-chip memory, incurring once again n(n-1) compulsory shifts and n(n-1) overhead shifts. Bearing in mind that the tensor C consists of  $T_1T_3$  tiles, adding all of these shifts to Equation (11) yields

$$T_{1}T_{2}T_{3} \cdot (2n^{3} - n^{2} - n) +T_{1}T_{2}T_{3} \cdot 2n(n-1) +T_{1}T_{2}T_{3} \cdot 2n(n-1) +T_{1}T_{3} \cdot 2n(n-1) +T_{1}T_{3} \cdot 2n(n-1) +T_{1}T_{2}T_{3} \cdot (n^{2} - n) +T_{1}T_{2}T_{3} \cdot 2n(n-1) +T_{1}T_{3} \cdot 2n(n-1) +$$

Although the number of overhead shifts only grows quadratically with n, for a fixed n they can still accumulate to a noticeable number. We eliminate them by judiciously laying out tiles that are newly brought into the SPM. Instead of restoring the positions of access ports to location 0 before and after loading/writing each tile, the rows and columns of tiles are loaded and processed in a back-and-forth manner, completely analogous to our discussion in Section 3.3. This completely removes the shifting overhead caused by tiling. Furthermore, the initialization of a tile of C with zeros can take place at the same time as the writing back to off-chip memory of the previously computed tile. Thus, the final total number of shifts required for tiled tensor contraction in the RTM-based SPM is

Total shifts (opt)<sub>tiled</sub> =

$$T_1 T_2 T_3 \cdot \{2n^3 + n^2 - 3n\}$$

+  $T_1 T_3 \cdot \{n^2 - n\}.$  (12)

#### 3.5 Hiding Tile-Switch Latency with Prefetching

For large tensors, as soon as the result of contracting the current tiles of *A* and *B* has been computed, these tiles need to be replaced, requiring  $2n^2$  off-chip reads. In addition, after every  $T_2$  tiles, the contents of the resultant tile of *C* must also be written back to the off-chip memory, incurring another  $n^2$  off-chip writes. For the access latencies, let us assume that the off-chip access latency, including the data transfer, is  $t_{off}$  and both the off-chip memory and the SPM are read/write symmetric. The *tile-switch* latency then becomes

Tile-switch latency =

$$\beta + \begin{cases} 2n^2 \times t_{\text{off}}, & \text{every tile,} \\ 3n^2 \times t_{\text{off}}, & \text{after every } T_2 \text{ tiles,} \end{cases}$$

(13)

where  $\beta$  represents the transfer initiation cost. Since the off-chip latency  $t_{\text{off}}$  is significantly higher than the access latency of the SPM, the tile-switch latency contributes significantly to the total latency and can thus pose a serious performance problem. The value of  $\beta$  and  $t_{\text{off}}$  are not fixed and depends upon memory layout, memory access schedule, and memory access granularity (cf. Section 4).

To reduce the impact of the off-chip latency on the embedded system's performance, we can use compiler-guided prefetching to overlap the off-chip access latency with the computation latency. Specifically, as soon as the computation of the first row in the resultant tile has been completed, the first row of  $\tilde{A}$  can already be replaced with the elements of the new tile. This replacement can happen while the processing unit operates on the next row of  $\tilde{A}$ . Thus, the load latency of  $\tilde{A}$  can be overlapped with the computation latency. Since every element in the resultant tensor requires n scalar multiplications and n - 1 additions, computation of the entire row of the resultant tile provides sufficient time for accessing n elements from the off-chip memory.

When the computation of the last row of the resultant tensor *C* starts, some of the rows in the next tile of  $\tilde{A}$  have already been loaded into the SPM. The compiler can then start prefetching the remaining rows of  $\tilde{A}$  and the columns of the next tile of  $\tilde{B}$ . One new column of  $\tilde{B}$  can be loaded into the SPM after the computation of each entry in the last row of *C*. After computing the last entry in the resultant tile of *C*, the processing unit can immediately start multiplying the first row in the next tile of  $\tilde{A}$  with the first column in the next tile of  $\tilde{B}$ . This way, the significant tile-switch latency can be reduced by overlapping it with computations. In Section 4, we explain how data from the off-chip memory can be efficiently accessed to improve performance and energy.

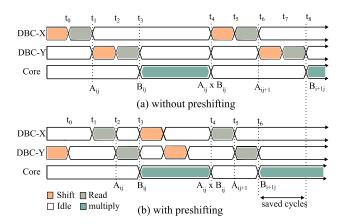

#### 3.6 Overlapping Shift and Compute Latency with Preshifting

In Section 3.3, we described an optimized memory layout and access order that incurs zero overhead shifts. In Section 3.5, we introduced prefetching to completely hide the tile-switch latency

Fig. 7. Overlapping shift latency with computation (DBC X and Y store the elements of A and B, respectively).

(for off-chip memory accesses) by overlapping the loading of tiles with the computation process. In this section, we explain how preshifting optimizes the access latency of the on-chip RTM-based SPM.

Typically, SRAM-based SPMs have a fixed access latency of one cycle. Since RTMs are sequential in nature, even with the best memory layout, the DBCs in RTM-based SPM must be shifted once before the next entry can be accessed. This shifting typically takes one cycle, and another cycle is needed to read out the next entry. Hence, the access latency of the RTM-based SPM is 2 cycles.

Fortunately, in the case of tensor contractions, the access pattern is known and the compiler can accurately determine the next memory location to be accessed. We take advantage of this and completely hide the shift latency by *preshifting*, an operation that aligns the access ports of the active DBCs with the memory locations to be accessed next. For instance, when the processing unit is busy multiplying  $\tilde{A}_{00}$  with  $\tilde{B}_{00}$ , both DBCs storing the current row and column are preshifted to point to the next entries, i.e.,  $\tilde{A}_{01}$  and  $\tilde{B}_{10}$ . The next memory request made by the program will ask for these entries, and the ports will already be aligned to positions of  $\tilde{A}_{01}$  and  $\tilde{B}_{10}$  in their respective DBCs. This effectively hides the shift overhead and halves the SPM access latency, as illustrated in Figure 7. Note that this does not interfere with the prefetching operation which affects different DBCs.

#### 3.7 Code Generation for Tensor Contractions

The memory layout and access order that we have identified to reduce the number of shifts in tensor contractions can be automatically generated by a compiler. This includes the appropriate handling of tiling, and even the prefetching and preshifting operations. The major complication in getting a compiler to automatically generate efficient code for tensor contractions is the detection of contractions in the program source code. For programs written in a general-purpose language, this is a non-trivial task: the way in which loop nests and multi-dimensional tensor accesses are structured may obscure the true nature of a tensor operation.

Previous work has suggested methods for detecting matrix multiplication and, more recently, tensor contraction in programs written in general-purpose programming languages. For the Fortran programming language, this is described in [36]. A suggestion for detecting tensor contractions in general-purpose languages has been made in [16], relying on polyhedral methods for the analysis of loop nests [15]. To the best of our knowledge, no assessment exists of how effective

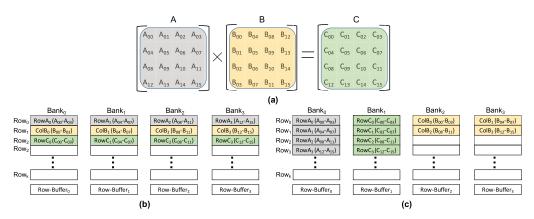

Fig. 8. (a) Illustrative example, (b) naive memory layout, (c) contention-aware memory layout.

the described detection techniques are in detecting contractions in real application domains such as signal and media processing, computer vision, and machine learning.

Domain-specific languages (DSL), on the other hand, offer an alternative approach that makes the nature of domain-specific operations, such as tensor contraction, obvious to the compiler or, more generally, to any code analysis. This is achieved by making tensor contraction a primitive operation of the language, as is the case in virtually all DSLs that are in wide-spread use in the area of machine learning [1, 5, 45]. In the form of MATLAB/Simulink, DSLs are also commonly used in the signal-processing domain. Note that the method for detecting matrix multiplication in [36] is also applicable to MATLAB programs. New DSLs for signal processing [46, 49] have recently been developed, in particular also for embedded applications [32].

In the area of scientific computing, DSLs for tensor operations have been in use for some time, e.g., [4]. Continued interest and recent new developments in this area show that DSLs for tensors are a practically relevant approach to increasing programmer productivity and application performance [30, 47].

### 4 OFF-CHIP LAYOUT AND ACCESSED ORDER FOR IMPROVED PERFORMANCE AND ENERGY CONSUMPTION

This section describes how an optimized SPM access data from the off-chip DRAM in a performance and energy-friendly way. The proposed optimizations for the off-chip DRAM include: a contention-aware memory layout, an intelligent memory access schedule, and the choice of a suitable memory access granularity. Further, we discuss the impact of these optimizations on the overall energy consumption of the DRAM memory.

#### 4.1 Contention-Aware Memory Layout

To explain our contention-aware memory layout, we consider an illustrative example showing  $A \times B = C$  in Figure 8(a). For the given example, we make the following assumptions. Each tensor consists of 16 elements (i.e.,  $A_{00}$  to  $A_{15}$  for tensor A and  $B_{00}$  to  $B_{15}$  for tensor B) and each tensor fits into its corresponding SPM bank. The off-chip DRAM has 4-banks while each bank has its row-buffer (see Figure 8(b)). For instance, the Row-Buffer<sub>0</sub> in Figure 8(b) can accomodate any Row<sub>i</sub> of Bank<sub>0</sub>. We further assume that each DRAM row stores four elements. For instance, Row<sub>0</sub> of Bank<sub>0</sub> in Figure 8(b) accomodates the first row of tensor A and so on. We start with a naive layout in Figure 8(b) where tensors are mapped to different banks in a row/column interleaved fashion. In

Table 1. Comparing Naive Memory Layout (Figure 8(b)) and Contention-Aware Optimized Memory Layout (Figure 8(c)) for Sequence of Read Commands to Compute the Result of  $C_{00}$  Using the (a) Naive Schedule and the (b) Contention-Aware Schedule

| Naïve-schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Naïve-Mem-layout    | CA-Mem-layout                              | CA-schedule          | Naïve-Mem-layout                           | CA-Mem-layout                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------|----------------------|--------------------------------------------|--------------------------------------------|

| Load A <sub>00</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $ReadRow_0ofBank_0$ | $ReadRow_0ofBank_0$                        | Load A <sub>00</sub> | Read $Row_0$ of $Bank_0$                   | Read Row <sub>0</sub> of Bank <sub>0</sub> |

| Load B <sub>00</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $ReadRow_1ofBank_0$ | $ReadRow_0ofBank_2$                        | Load A <sub>01</sub> | Read Row <sub>0</sub> of Bank <sub>0</sub> | Read Row <sub>0</sub> of Bank <sub>0</sub> |

| Load A <sub>01</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $ReadRow_0ofBank_0$ | $ReadRow_0ofBank_0$                        | Load A <sub>02</sub> | Read Row <sub>0</sub> of Bank <sub>0</sub> | Read Row <sub>0</sub> of Bank <sub>0</sub> |

| Load B <sub>01</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $ReadRow_1ofBank_0$ | $ReadRow_0ofBank_2$                        | Load A <sub>03</sub> | Read Row <sub>0</sub> of Bank <sub>0</sub> | Read Row <sub>0</sub> of Bank <sub>0</sub> |

| Load A <sub>02</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $ReadRow_0ofBank_0$ | $ReadRow_0ofBank_0$                        | Load B <sub>00</sub> | $ReadRow_1ofBank_0$                        | Read Row <sub>0</sub> of Bank <sub>2</sub> |

| Load B <sub>02</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $ReadRow_1ofBank_0$ | $ReadRow_0ofBank_2$                        | Load B <sub>01</sub> | Read $Row_1$ of $Bank_0$                   | Read Row <sub>0</sub> of Bank <sub>2</sub> |

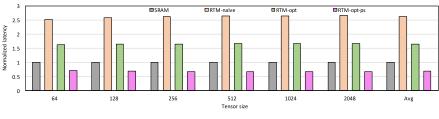

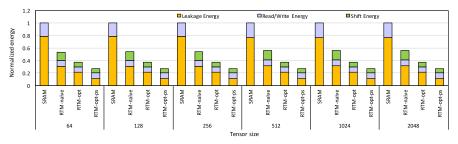

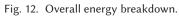

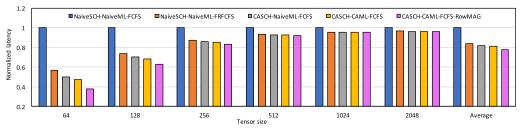

| Load A <sub>03</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $ReadRow_0ofBank_0$ | Read Row <sub>0</sub> of Bank <sub>0</sub> | Load B <sub>02</sub> | Read $Row_1$ of $Bank_0$                   | Read Row <sub>0</sub> of Bank <sub>2</sub> |